With the introduction of the complex on-chip power management techniques , there is an increase in the possibility of a design error that can be destructive if the false current paths are not detected and properly controlled and thus imposes a challenge in the verification of the design.On chip power management is fundamentally an analog/mixed signal problem , demanding analysis of both analog and digital circuit behavior.

For every power management technique there is a need for both dynamic verification and static verification.While

dynamic verification is a test vector based verification to validate the functionality of the design;

static verification is a vector less approach which performs structural and architectural checks of the design.

Verify Multi Voltage Design:

Prior to MV design technique, every design had two power states ON state and an OFF state , as the design works on single Supply voltage. This made the verification easy as the whole design understands the boolean logic '0' and '1' for the same voltage level.

With the MV design technique included in the design, apart from the ON/OFF states,there are more n different combination of power states included based on the different voltage supplies used inside the design , thus increasing the number of power states and their transitions.This also defines different voltage levels for '0' and '1' in different blocks of the design. Thus while we verify the signal interface between different voltage domain blocks,it's not the boolean value validation but the voltage levels of the signals that needs to be validated.

Level shifters should be taken into account during the logic conversion of signals from one voltage domain to another.

Apart from this there is a need for a Voltage aware verification to verify the MV islands in the design.

1.

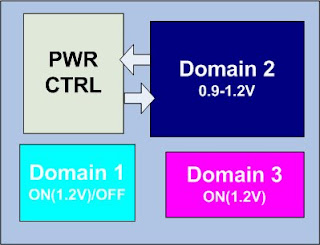

For example, In the above figure we can see there are three voltage domains with different power modes/states that is defined by the voltage at which each domain is working.Here we need to ensure that the Memory content is not lost when the supply rail falls below the standby voltage for that particular voltage domain.

2.In case of DVFS(Dynamic Voltage Frequency scaling)

, since voltages are changed during run time,we need to check that the voltage ramp times are carefully controlled to avoid voltage overshoot or undershoot which can lead to the malfunctioning of the system.

3.Apart from the mentioned scenarios , there is also a need to perform static verification checks to validate

a. Level shifters by providing a separate constraint for each supply voltage level

b. If the power switch control signals are generated from appropriate domains.

c. Clock tree(to verify the clock swings from one voltage domain to another voltage domain)

d. Reset signals for the design

e. Finally timing checks for a block operating at different voltages(different voltages can

demand the same block to meet different performance objectives) by performing static

timing analysis.

Power Gating:Unlike multi-VDD , power gating demands a Power-Aware verification as in a power gating technique various blocks in the design are completely shut-off /on based on the control signals coming from Power controller.For all those blocks with the power gated logic implemented, we need to verify two major states for that block in the design the Power Up and Power Down state, which cumulates into a set of power states for the design to operate.

Now, Let's look at the major challenges that come along with power-gating :

1.

Power states: To verify the functionality of the design in every power state.;

2.

Power State transitions: To verify the functionality of each block in the design while the design transits from one power state to another to ensure all legal state entry and exist.

3.Valid Power sequences: The power sequence is mainly to ensure the right voltage switches are ON for a particular block in the design.Here we need to validate

a. All power domains are completely powered up before issuing reset.

b. Main control unit of the design doesn't power up until entire chip is powered up.

For example , in the below figure we can see three power domains with its respective power table intent showing the power states and their transitions.

4. To ensure that the powered down block does not evaluate the events of the input transitions to the block .This can be evaluated by checking that there are no transitions on the inputs of the always-on block coming from the power gated block.

5. The pass through wires of a powered down logic are not affected, i.e. there can be a set of wires routed through the powered down logic , the logic of these wires should remain unaffected.

6. On powering up the power gated blocks,need to verify that the logic behavior in the block is enabled for evaluation, i.e. combinatorial logic and latches are re-evaluated,continuous assignments are re-evaluated and edge triggered logic of the flops are evaluated on next active edge.

7. To verify the power up sequence that powers up and down the various blocks in the design and the acknowledgment thus received.

8. To verify that the power gated block doesn't resume it's operation until the switching fabric is completely powered up.

9. If same power rail is used for external switching and internal switching , then need to verify the always-on logic which might remain off during external switching.

10. To detect the wastage of power in the design:

For example toggling of clock when power domain is in OFF state.

11 .There's also a need to emulate the IR drops and analyze the circuit behavior for the same.

Verifying Retention :

1. There is a need to verify that proper timing of the control signal (

SAVE) is provided for the retention registers to save the values of those registers required before powering down.Improper timing can lead to corrupted data storage.

2. There is a need to verify that the proper timing of control signals(

RESTORE) are provided to the retention registers to restore the values of those registers required on power up.Improper timing would end up in trying to restore the values before the registers intended are not powered up.Thus malfunctioning of the circuit.

Apart from this neither clock nor reset should be provided to the power gated block while the retention registers are saving/restoring the information.

3. If the power gated block is employing partial retention, functional testing is required to ensure that there are no illegal combination states that might cause deadlock.

For example:In order to allow the powered down block to restart correctly , the non-retention registers are fed with X values.So there is a need to verify that the non-retention registers are corrupted during power down and remain corrupted even after power up until the controlling logic is re-evaluated.Here there is also a need to verify that on power up of the block, the X values in the non-retention registers doesn't propagate and affect the function of the circuit.

4.Need to verify the X's are not propagated once the power gated block is restarted.

5. Retention registers in a block are properly connected and remain always-on and are not effected by either power-up or power-down of the respective block.Improper power supply connection will lead to loss of data storage.

Verifying Isolation :

1. To verify the unintentional propagation of high impedance states from power gated block to the always-on block.This mainly comes under static verification in structural checks to look for missing isolation cells in the design

2. Isolation logic of the particular power domain is also properly connected to the isolation power and ground and remains untouched by the power gated block.Improper power supply connection will lead to transmission of undesired signals.

3. Need to verify multiple net condition for the outputs of isolation cells while pull-up and pull-down clamps are used as isolation cells.

4. To verify that the domain of the control signals that are provided to the isolation cell are buffered by the always-on buffers.

5. Verify stuck at '1' and stuck at '0' at the output of the isolation cell.

Assertions should be provided at the power gating controller ports to ensure that the required switching technology, the above mentioned functionality and coverage are met.The power gating control signals should be controllable while testing .

Having said thus, all these and most of them form part of the functional check of the design where the functionality of the design has to be checked against various control signals generated by a power controller unit in the design,power switches,various domain interfaces that include the isolation cells,retention registers,ELS and level shifters.But then, all these do no exist in the RTL(and thus the control signals remain floating) and later during synthesis, the tool smartly adds these cells .

In order to emulate the behavior of those cells for simulation, one of the possible solution is PLI's. But then, the major concern here is there should be two RTL's , one with PLIs to simulate the behavior and one without PLIs for synthesis.

In order to combat this huge burden that comes with the complex designs and more of power saving strategies ahead,UPF standard has been introduced that helps in capturing the power intent of a design that goes through the entire flow of a design for both verification tool and the Implementation tool.